Sigo esperando mis registros de desplazamiento 74HC595 de 8 bits, así que se me ha ocurrido hacer un tutorial sobre él, pero como no lo tengo aun voy a hacer uno sobre registros en general, pero dado que los registros están formados por biestables, voy a hacer antes un tutorial sobre biestables, o sea, este.

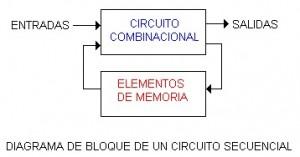

Los biestables son circuitos secuenciales, es decir, son capaces de almacenar información, ya que las salidas son función de la combinación de las entradas y los datos almacenados en memoria, que a su vez pueden cambiar en función de las entradas.

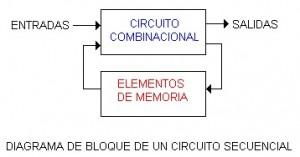

Un circuito secuencial dispone de un bloque secuencial formado por elementos de memoria que almacenan bits, y un bloque combinacional que recibe las entradas del circuito secuencial y los valores almacenados en los elementos de memoria y genera las salidas y los próximos valores a almacenar en memoria.

BIESTABLES

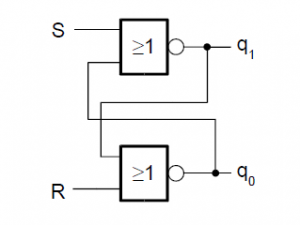

-SR con puertas NOR

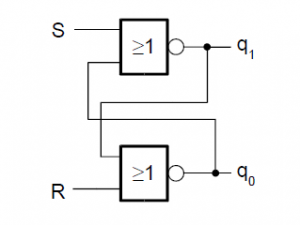

Cuando se activa S (Set) con un 1, en la salida del biestable se genera un 1, si se activa R (Reset) con un 0, se provoca el borrado del biestable. si ninguna de estas entradas estan activas, el biestable almacena el valor (1 o 0) escrito anteriormente. Es evidente, que S y R no deben estar activas simultáneamente.

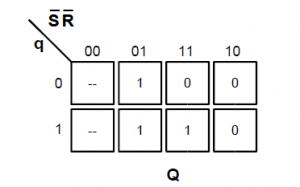

Las salidas q0 y q1 depende de S y R y de si mismas. Dado que las puertas NOR introducen un cierto tiempo de propagación, podemos distinguir los valores q0 y q1 que tomará de entrada con los valores q0 y q1 que tomará de salida cuando pase este tiempo de propagación. Por lo que llamaremos a esos valores futuros Q0 y Q1 y a los actuales q0 y q1.

La salida S provoca la escritura de un 1 en el biestable y la R la de un 0, y si ninguna esta activa el biestable mantiene su valor.

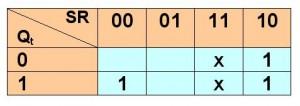

Los biestables SR tienen las siguientes restricciones:

– Las entradas SR=11 quedan prohibidas, ya que el biestable entra en un situación oscilatoria.

– La duración de los pulsos Set y Reset debe ser superior a 2xT para que las salidas q0 y q1 tomen un valor estable adecuado.

Si se cumple esto, las salidas nunca tomarán el valor 00 ni 11, además el biestable tiene una salida q que muestra el valor almacenado y q negado que muestra el valor complementado.

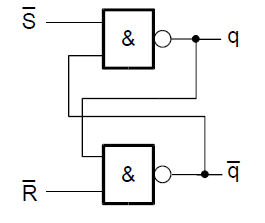

-SR con puertas NAND

Cualquier circuito que se pueda hacer con puertas NOR se puede hacer con puertas NAND

BIESTABLES SINCRONOS

Los biestables anteriores eran ásincronos, es decir, no tienen ningún mecanismo que permita su sincronización, esta viene dada por una línea adicional, llamada línea de reloj, que indica al biestable cuando puede cambiar de estado, es decir, cuando puede cambiar sus salidas.

El uso de biestables síncronos minimiza el riesgo de que se den azares y oscilaciones.

Cuando un biestable síncrono esta habilitado es debido a la señal de reloj, que normalmente será una señal binaria, periódica, cuadrada y alterna.

Existen varios tipos de biestables:

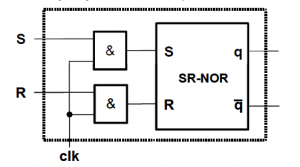

-Disparados por nivel:

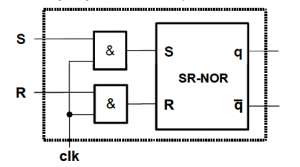

Este está constituido por un biestable SR-NOR (biestable asíncrono), dos puertas AND cuyas salidas controlan las entradas SR del biestable asíncrono y cuyas entradas son S y R, y la señal de reloj clk.

Si clk=0, las salidas de las puertas AND son 0 y SR son 00, por lo que el biestable no cambia de estado. Esto es así independientemente de los valores de SR. Si clk=1, las entradas SR actúan directamente sobre el biestable asincrono y este cambiara de estado según los valores de dichas entradas.

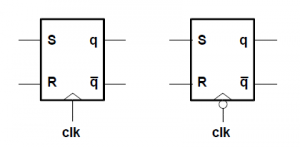

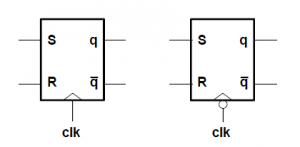

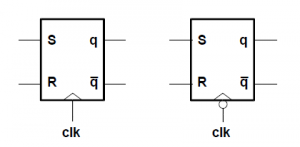

Hay dos tipos de biestables disparados por nivel: nivel bajo y nivel alto.

El primero es disparado por nivel alto, es decir, clk=1 habilita el biestable, el segundo es disparado por nivel bajo, es decir, clk=0 habilita el biestable.

-Biestable Maestro-Esclavo

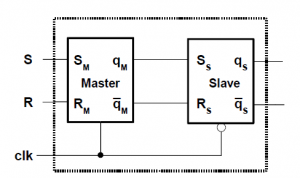

En ocasiones es interesante que los cambios de estado se realicen en instantes muy determinados.

Para esto usamos dos biestables disparados por nivel, donde las salidas del maestro son las entradas del esclavo, y donde solo uno de los dos puede estar activo a la vez por ciclo de reloj, por lo que uno debe ser disparado por nivel alto y el otro por nivel bajo, estando activo en el siguiente ciclo de reloj el que estaba inactivo y viceversa.

-Disparados por el flanco:

Su funcionamiento es similar al maestro-esclavo, ya que la salida q solo cambia en el flanco de subida o en el flanco de bajada.

En el flanco activo (bajado o subida) se leen las entradas que determinan el valor de q para el siguiente ciclo de reloj.

Al inicio, el valor de q es desconocido hasta que llegue su flanco activo.

OTROS BIESTABLES

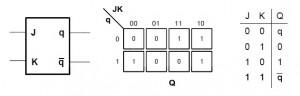

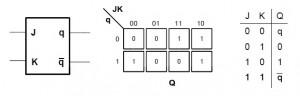

-Biestable JK: Similar al SR pero J=K=1, es decir JK=11 no está prohibida.

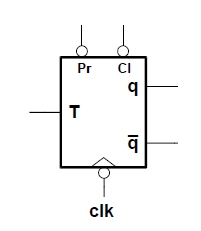

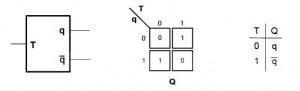

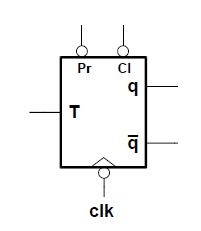

-Biestable T: Igual que el JK pero unimos sus entradas

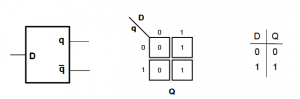

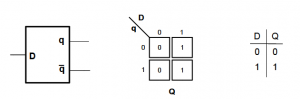

Biestable D: Almacena el bit que llega por su única entrada

ENTRADAS ASINCRONAS DE LOS BIESTABLES

Son entradas adicionales de las que disponen algunos biestables síncronos- Estas entradas permiten poner el estado a 0 o 1 sin necesidad de esperar a llegar al nivel o flanco activo de la señal de reloj.

Estas entradas son Preset (Pr) y Clear (Cl),la primera pone q a 1 y la segunda a 0. Pueden estar activas en alto o en bajo.

Obviamente no tiene sentido activar ambas entradas a la vez, en tal caso tomaremos solo una como activa.

Si hay un disparo del biestable justo con una entrada asíncrona activa, ese disparo no tiene efecto.

style="display:inline-block;width:728px;height:15px"

data-ad-client="ca-pub-3868159888315364"

data-ad-slot="7639712738">

I keep waiting for my 8-bit shift registers 74HC595, so it occurred to me to do a tutorial about it, but i haven’t it yet, so I’m going to do one about registers in general, but registers are formed by flip-flops, I will do a tutorial about flip-flops before , ie this.

The flip-flops are sequential circuits, ie , are capable of storing information, and the outputs are a function of the combination of the inputs and the data stored in memory, which may change depending on the inputs.

A sequential circuit has a sequencial bloc of memory elements that store bits, and a combinational block which receives inputs of the sequential circuit and the values stored in the memory elements and generates the outputs and the next values to be stored in memory.

FLIP-FLOPS

-SR with NOR gates

When S (Set ) is activated with a 1, at the output of flip-flop is produced a 1, if R (Reset) is activated by a 0 , the erasure of the bistable is raised. If any of these inputs are active , the flip-flop stores the value ( 1 or 0) written above. It is evident that S and R should not be active simultaneously.

The q0 and q1 outputs depend on S and R and of themselves. Since the NOR gates introduce a propagation time , we can distinguish the values q0 and q1 that inputwill take with q0 and q1 values that output will take when this propagation time pass out. So we will call those future values Q0 and Q1 and current q0 and q1.

The output S causes writing a 1 in the bistable and the R a 0 , and if none is active flip-flop holds its value.

SR flip-flops have the following restrictions:

– SR = 11 entries are prohibited , since the flip-flop would enter in oscillatory situation.

– The duration of the Set and Reset pulses must exceed 2xT so that q0 and q1 outputs take a suitable stable value.

If this is true , the outputs will never take the value 00 or 11, also flip-flop has an output q showing the stored valueand q denied showing complemented value.

-SR with NAND gates

Any circuit that can be done with NOR gates can be done with NAND gates.

SYNCHRONOUS FLIP-FLOPS

The latest flip were asynchronous , ie , they have no mechanism for synchronization , this is given by an additional line called clock line , indicating the flip-flop when it can change state , ie , when it can change their outputs.

The use of synchronous flip minimizes the risk that hazards and oscillations occur.

When a synchronous flip-flop is activated is becauseof a clock signal, which will normally be a binary , periodic , square and alternating signal

Several types of flip-flop:

-Fired by level:

This is constituted by a bistable SR- NOR (bistable asynchronous) , two AND gates whose outputs control the asynchronous SR flip-flop outputs and whose inputs are S and R , and the clock signal clk.

If clk = 0 , the outputs of the AND gates are 0 and SR is 00 , so that the flip-flop does not change his state.This is true regardless of values of SR . If clk = 1, SR inputs act directly on the asynchronous flip-flop and it changes his state according to values of these inputs

There are two types of level -triggered flip-flops : low level and high level.

The first is shot high level , ie , clk = 1 enables the flip-flop , the second is shot by low level , ie , clk = 0 enables the flip-flop.

-Master-Slave Flip-Flop

Sometimes it’s interesting that state changes are made in very specific moments.

For this we use two level shot flip-flops , where the outputs of the master one are the inputs of the slave one, and where only one of the two can be active at a time per clock cycle, so one must be triggered by high level and other by low level, being active in the next clock cycle which was inactive and vice versa.

-Flank fired:

Its operation is similar to the master -slave because the q output only changes in rising edge or in falling edge.

In active edge (down or up) inputs that determine the value of q for the next clock cycle are read.

Initially, the value of q is unknown until first active edge.

OTHER FLIP-FLOPS

-JK flip-flop : Similar to SR but J = K = 1 , ie JK = 11 is not prohibited.

-T Flip-flops: Same as JK but we joined his inputs.

-D flip-flop: Stores the bit that comes by its unique input

FLIP-FLOPS ASYNCHRONOUS INPUTS

They are additional inputs taht some flip-flpos have. These inputs allow state setting to 0 or 1 without waiting to reach level or active edge of the clock signal.

These inputs are Preset (Pr) and Clear ( Cl ), the first puts q to 1 and the second to 0. They can be active high or low.

Obviously it has no sense to activate both inputs at once, in which case we will take only one active.

If there is a fair shot of the flip-flop with an active asynchronous input , the shot has no effect.

style="display:inline-block;width:728px;height:15px"

data-ad-client="ca-pub-3868159888315364"

data-ad-slot="7639712738">