Hoy, siguiendo con varios artículos más que hablan de la arquitectura del computador, voy a hablaros del efecto conocido como “memory wall”. Anteriormente hablé de la Ley de Moore, o la Ley de Amdahl, ambos relativos al rendimiento del PC, y éste artículo va en la misma línea, ya que es el principal campo de investigación de la Arquitectura de computadores.

El memory wall es un efecto que se produce por una disparidad de la evolución entre la velocidad de la CPU (procesador) y la memoria que se encuentra fuera del chip de la CPU. Entre 1980 y 2005, la velocidad de la CPU mejoró un 55% cada año, mientras que la velocidad de la memoria lo hizo solo un 11%. Parte de esta disparidad es debida a la limitación del bus que comunica la memoria con la CPU. Por este motivo se esperaba tener un cuello de botella en la evolución del rendimiento del computador dada por la velocidad de memoria.

Debido a esta compleja problemática, se han debido desarrollar diversas soluciones que permitan aumentar el rendimiento. También es necesaria gran capacidad, ya que hay que almacenar en memoria programas de tamaño creciente para poder ejecutarlos. Como dijo Von Newman, creador del modelo del computador que conocemos hoy en día:

Idealmente, desearíamos tener una cantidad infinita de memoria con un tiempo de acceso inmediato.

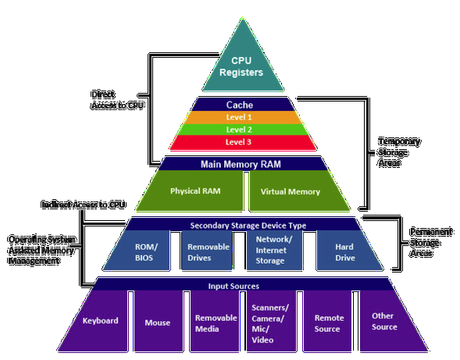

Sin embargo, ambas características son totalmente opuestas, ya que una memoria de mayor capacidad presenta un menor rendimiento, ya que aumenta la latencia del direccionamiento. Por éste motivo se ha diseñado un sistema de jerarquía de memorias, en el cual se consigue el efecto de tener gran cantidad de memoria muy rápida. Este sistema de jerarquías funciona en forma de niveles, siendo los niveles inferiores más cercanos al procesador y de menor tamaño, permitiendo una velocidad similar a la de éste, y los niveles superiores de mayor tamaño y más lentos.

De ésta forma, los niveles inferiores tienen los datos que se van a utilizar más pronto, o más a menudo. Los niveles superiores van conteniendo más cantidades de datos cada vez. Los datos del nivel inferior son un subconjunto de los datos del nivel superior, de forma que se mantiene una coherencia entre todos ellos. Para ésto existen unos algoritmos de mapeo de las direcciones de memoria de los niveles superiores en los niveles inmediatamente inferiores. Igualmente existen varios mecanismos de escritura cuando los datos son modificados en el nivel inferior, para propagar dicho cambio entre todos los demás niveles. Igualmente existen varios algoritmos para decidir qué datos son más apropiados para mantener en los niveles más inferiores, y cada fabricante lo implementa de una forma, tratando de dar el mayor rendimiento posible a su sistema en conjunto.

Típicamente, un sistema de hoy en día, tiene dos tipos de memoria: la memoria caché y la memoria RAM. Los niveles se organizarían del siguiente modo: caché de nivel 1 (L1), caché de nivel 2 (L2), caché de nivel 3 (L3), caché de nivel 4 (L4), la memoria RAM y, por último, el disco duro. Cuando se va a buscar un dato al L1 y no se encuentra, entonces se pasa a buscarlo al L2, si no se encuentra se para a L3, y así sucesivamente. Cuando el dato es encontrado, se va subiendo en la jerarquía de memoria nivel a nivel, hasta el L1, desde donde pasa al procesador.

Existen múltiples técnicas que se han utilizado para la gestión y mejora del rendimiento en la jerarquía de memorias, pero éste es un tema muy específico y extenso que no se puede explicar en un único artículo. Sin embargo ya os habéis hecho una idea del funcionamiento con éste artículo.

Pero antes he hablado de que, además de la limitación de la latencia de acceso a memoria dada por el tamaño de ésta, también existe la limitación del bus que comunica la memoria con la CPU. Ésto típicamente es un problema para los accesos L3 e inferiores, pues, por lo general, los fabricantes suelen alojar la memoria de los niveles L1 y L2 dentro del propio procesador. Para solventar en parte esta limitación, en Intel han desarrollado una tecnología que han llamado 3D stacking, y que permite acercar la memoria a la CPU. La explicación del funcionamiento de ésta tecnología es suficiente para un artículo aparte, por lo que no voy a continuar con ello.

Espero haberos ayudado a comprender un poco más el funcionamiento de vuestra máquina por dentro y os animo que que podéis investigar algo buscando en Internet acerca de estos temas, si estáis interesados. También podéis comentar para preguntar si algo no os parece claro o para corregir si entendéis y creéis que me he equivocado en algo.

El artículo El Memory wall y la jerarquía de memorias apareció por primera vez en Instinto Binario.

LOS COMENTARIOS (2)